§ Регистр IR

Регистр IR (Instruction Register) - 16 разрядный. В старших байтах его содержится код операции (их всего 8), src и dst операнд, а в младших содержится D - данные, которые могут быть либо непосредственным операндом, либо указателем на ZP, либо участвовать в процессе условного и безусловного перехода.

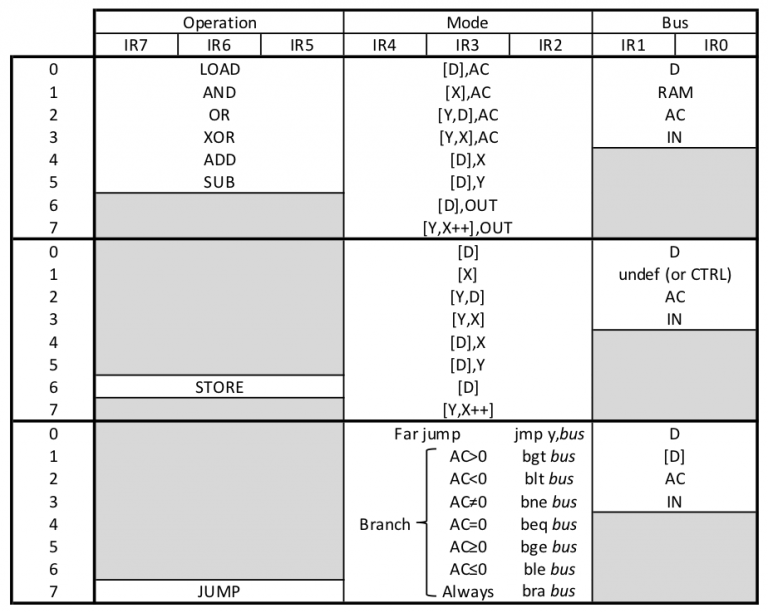

IR7 IR6 IR5 | IR4 IR3 IR2 | IR1 IR0 (bus) | D7..D0

--------------+---------------+-----------------+--------

Код операции | Операнд DST | Операнд SRC | Данные

| (mode) Режим | D,[RAM],AC,IN |§ Коды операции

000 0 LOAD Загрузка из src 001 1 AND Логическое поразрядное "И" над dst & src 010 2 OR Поразрядное "ИЛИ" 011 3 XOR Поразрядное "Исключающее ИЛИ" 100 4 ADD Сложение dst+src 101 5 SUB Вычитание dst-src 110 6 STORE Сохранение src в dst 111 7 JUMP Условный или безусловный переход

§ Арифметическо-логические операции

Для операции LOAD,AND,OR,XOR,ADD,SUB действует единая система распознавания операндов. Первый операнд всегда аккумулятор.- bus=0, используется в качестве операнда-источника (src) данные D в IR[7:0]

- bus=1, то тогда расшифровывается mode следующим образом:

000 0 [D] Адрес берется из data 001 1 [X] Из X 010 2 [Y,D] Старшая часть 16 битного адреса - Y, младшая часть - D 011 3 [Y,X] Старшая часть Y, младшая X 100 4 [D] Используется D 101 5 [D] ---//--- 110 6 [D] ---//--- 111 7 [Y,X++] Старшая часть Y, младшая X, но после считывания X увеличивается на единицуИз полученного адреса извлекается значение (из памяти) для операнда

- bus=2, источник равен AC

- bus=3, источник равен INREG (входящий регистр, аналог порта)

000 0 AC Аккумулятор AC 001 1 AC ---//--- 010 2 AC ---//--- 011 3 AC ---//--- 100 4 X Регистр X 101 5 Y Регистр Y 110 6 OUT Выходной порт OUT 111 7 OUT ---//---

§ Сохранение данных STORE

Операция STORE использует bus=0 (D), bus=2 (AC), bus=3 (INREG) в качестве операнда, который надо записать в память. Адрес памяти, которую необходимо записывать, вычисляется аналогично тому, что было при выборе памяти в АЛУ:000 0 [D] Адрес берется из data 001 1 [X] Из X 010 2 [Y,D] Старшая часть 16 битного адреса - Y, младшая часть - D 011 3 [Y,X] Старшая часть Y, младшая X 100 4 [D],X Используется D. Операнд-источник также пишется в X 101 5 [D],Y Используется D. Операнд-источник также пишется в Y 110 6 [D] Используется D 111 7 [Y,X++] Старшая часть Y, младшая X, но после считывания X увеличивается на единицуЗдесь есть отличие при выборе 4 и 5 режима, тогда помимо записи в память, данные из источника пишутся в X и Y соответственно.

§ Переход Branch

Операция перехода использует (mode) для того, чтобы выбрать, какой тип перехода будет использоваться:000 0 JMP Длинный переход, используется в качестве верхнего байта регистр Y, в качестве нижнего (src) 001 1 BGT A > B (AC^0x80) > 0x80 010 2 BLT A < B (AC^0x80) < 0x80 011 3 BNE A != B (AC^0x80) != 0x80 100 4 BEQ A == B (AC^0x80) == 0x80 101 5 BGE A >= B (AC^0x80) >= 0x80 110 6 BLE A <= B (AC^0x80) <= 0x80 111 7 BRA Переход выполняется всегдаПри этом стоит отметить, что при переходе старший байт адреса всегда будет равен старшему байту текущего указателя PC.

При проверке перехода используется обращение старшего бита AC, чтобы сравнить его с число 0x80. На основе этих данных, делается вывод, выполнять ли переход.

Интересной особенностью Гигатрона является то, что он при любом переходе все равно исполняет операцию, которая идет сразу за оператором перехода (условного или безусловного). Этот трюк позволяет извлекать данные из памяти ROM.

Если в качестве bus=1, то информация о переходе берется из памяти по адресу D.

§ Таблица инструкции