12:06

Драйвер семисегментного индикатора — Лисья нора

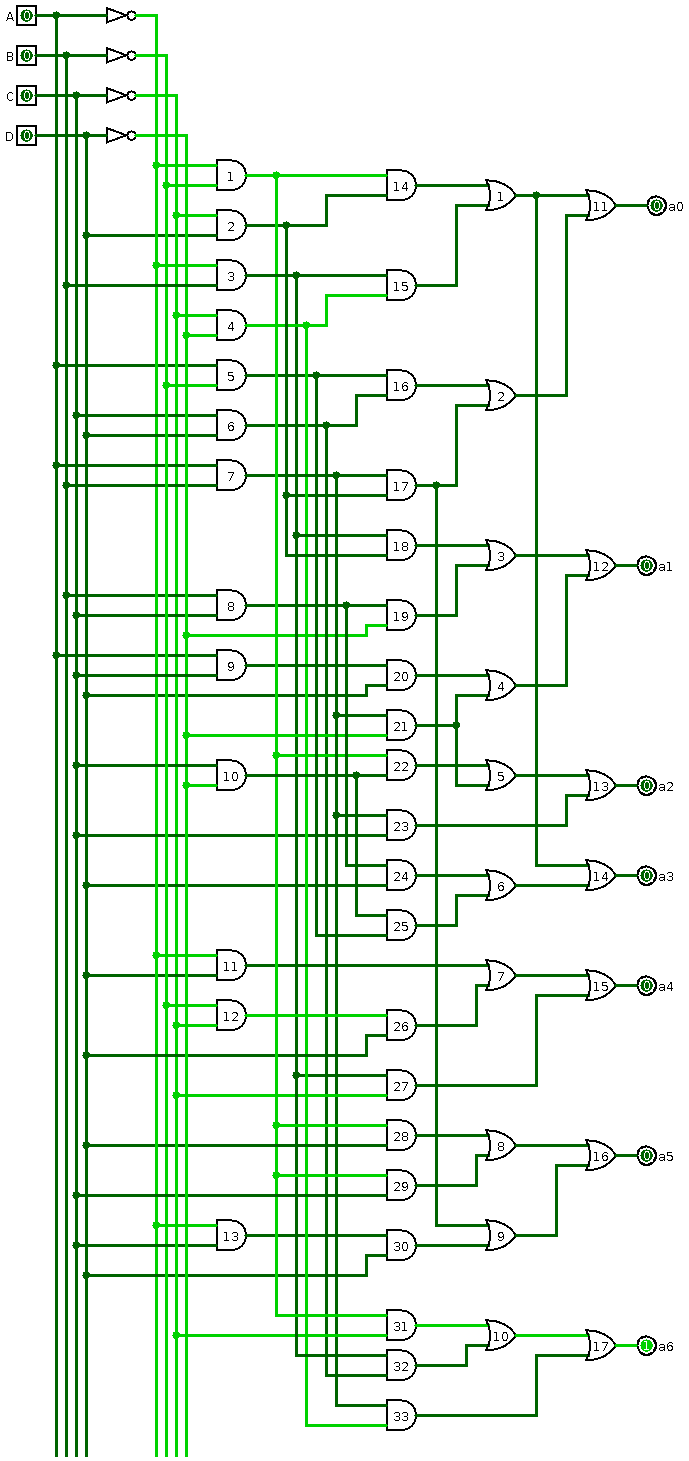

§ Комбинаторная схема

1 - Светодиод выключен (не горит)0 - Светодиод включен (горит)

HEX | 6543210 | DEC 0 -----+---------+----- ----- 0000 | 1000000 | 0 5 | | 1 0001 | 1111001 | 1 | | 0010 | 0100100 | 2 ----- 0011 | 0110000 | 3 4 | 6 | 2 0100 | 0011001 | 4 | | 0101 | 0010010 | 5 ----- 0110 | 0000010 | 6 3 0111 | 1111000 | 7 1000 | 0000000 | 8 1001 | 0010000 | 9 1010 | 0001000 | A 1011 | 0000011 | b 1100 | 1000110 | C 1101 | 0100001 | d 1110 | 0000110 | E 1111 | 0001110 | F

§ Код на verilog #1

- i - входящая цифра от 0 до 15

- o - инверсный выход, 0=горит, 1=не горит

module hex7 ( input wire [3:0] i, output wire [6:0] o ); // Сигнал на выход assign o = {o17, o16, o15, o14, o13, o12, o11}; // Инверсный вход wire [3:0] n = ~i; // Основная логика wire a1 = n[3] & n[2]; wire a14 = a1 & a2; wire o1 = a14 | a15; wire o11 = o1 | o2; wire a2 = n[1] & i[0]; wire a15 = a3 & a4; wire o2 = a16 | a17; wire o12 = o3 | o4; wire a3 = n[3] & i[2]; wire a16 = a5 & a6; wire o3 = a18 | a19; wire o13 = o5 | a23; wire a4 = n[1] & n[0]; wire a17 = a7 & a2; wire o4 = a20 | a21; wire o14 = o1 | o6; wire a5 = i[3] & n[2]; wire a18 = a3 & a2; wire o5 = a22 | a21; wire o15 = o7 | a27; wire a6 = i[1] & i[0]; wire a19 = a8 & n[0]; wire o6 = a24 | a25; wire o16 = o8 | o9; wire a7 = i[3] & i[2]; wire a20 = a9 & i[0]; wire o7 = a11 | a26; wire o17 = o10 | a33; wire a8 = i[2] & i[1]; wire a21 = a7 & n[0]; wire o8 = a28 | a29; wire a9 = i[3] & i[1]; wire a22 = a1 & a10; wire o9 = a17 | a30; wire a10 = i[1] & n[0]; wire a23 = a7 & i[1]; wire o10 = a31 | a32; wire a11 = n[3] & i[0]; wire a24 = a8 & i[0]; wire a12 = n[2] & n[1]; wire a25 = a10 & a5; wire a13 = n[3] & i[1]; wire a26 = a12 & i[0]; wire a27 = a3 & n[1]; wire a28 = a1 & i[0]; wire a29 = a1 & i[1]; wire a30 = a13 & i[0]; wire a31 = a1 & n[1]; wire a32 = a3 & a6; wire a33 = a7 & a4; endmodule

§ Код на verilog #2

Более сокращенный вариантmodule hex7 ( input wire [3:0] i, // Вход output wire [6:0] o // Выход ); assign o = ( // 6543210 i == 4'b0000 ? 7'b1000000 : // 0 i == 4'b0001 ? 7'b1111001 : // 1 i == 4'b0010 ? 7'b0100100 : // 2 i == 4'b0011 ? 7'b0110000 : // 3 i == 4'b0100 ? 7'b0011001 : // 4 i == 4'b0101 ? 7'b0010010 : // 5 i == 4'b0110 ? 7'b0000010 : // 6 i == 4'b0111 ? 7'b1111000 : // 7 i == 4'b1000 ? 7'b0000000 : // 8 i == 4'b1001 ? 7'b0010000 : // 9 i == 4'b1010 ? 7'b0001000 : // A i == 4'b1011 ? 7'b0000011 : // B i == 4'b1100 ? 7'b1000110 : // C i == 4'b1101 ? 7'b0100001 : // D i == 4'b1110 ? 7'b0000110 : // E 7'b0001110); // F endmodule

§ Логическая схема