§ Вступление

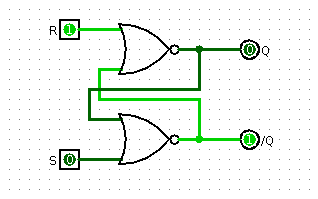

Помнится, я миллион раз рассказывал в видео своих, как работает триггер, но видео плохо сохраняются у меня, так что решил в тексте выразить. Начну вообще рассказ с самого простого триггера, который можно выполнить на 2 NAND, или на 2 NOR. Они совершенно идентично работают, просто в случае с NAND активный сигнал низкий (срабатывает на 0), а NOR — высокий (срабатывает на 1). Если что, NOR — это элемент ИЛИ-НЕ.

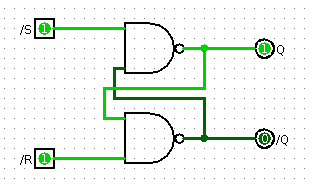

Рис 1. Схема триггера на 2И-НЕ (NAND)

§ Принцип работы

Триггер — это такое электронное устройство, которое запоминает последнее установленное состояние и не меняет его. В приведенной выше схеме есть один интересный момент. Допустим, что если мы сразу подадим две единицы на входы /S и /R. Так вот, зная о таблице истинности NAND, что по итогу выйдет?A B C 0 0 | 1 0 1 | 1 1 0 | 1 1 1 | 0Допустим, что на выходе у каждого элемента находится 1 как наиболее вероятное состояние, поскольку вероятность появления 1 равняется 75%. Хорошо. Что тогда получается?

На выходах NAND — две единицы. Так. На входах NAND — тоже две единицы! Это как так тогда? Этого просто быть не может. Почему? Потому что, если на входе NAND две единицы, то и на выходе будет 0.

Хорошо, представим себе, что на выходе появился 0 из-за того, что там две единицы было. Допустим, эти нули теперь появились на входах. Это значит, что на входе первого NAND будет 1 и 0, на выходе опять 1. И на втором тоже так же, 0 и 1 — и на выходе 1.

Получается какой-то зацикленный круг. Состояние 1 и 0 будет меняться с очень высокой скоростью, пока какой-либо сигнал из-за помех или ошибки не придет быстрее другого и не перебросится в стабильное состояние.

§ Фиксация на одном из состоянии

На рис.1 выше показана одна из фиксации, когда на проводе Q появляется 1, а на проводе /Q появлется 0 в результате электрической нестабильности, триггер переходит в одно из состоянии. Итак, что получается.1-й NAND (верхний) на входе 1 и 0, дает 1

2-й NAND (нижний) на входе 1 и 1, дает 0

Триггер находится в этом состоянии сколько угодно, потому что нет ничего, что может его перебросить. Точнее говоря, есть, но для этого надо поменять один из входов /S или /R на 0 вместо 1.

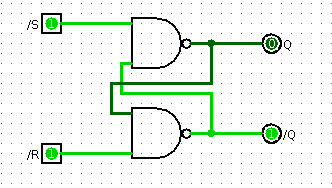

Аналогично, триггер может находится в другом состоянии:

Рис 2. Триггер в противоположном состоянии

Так же как ранее, триггер зафиксирован в этом состоянии и не двигается без внешнего воздействия.

§ Переключение состояния

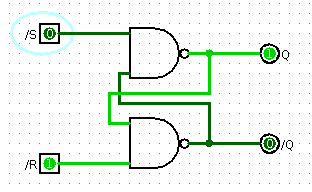

Теперь допустим, необходимо переключить из одного состояния в другое. Рассмотрим триггер на рис. 2.Шаг 1. Ставим 0 на входе /S вместо 1

Шаг 2. Теперь на верхнем NAND на входе 0 и 1, а значит, на его выходе появляется 1

Шаг 3. Следовательно, на входе нижнего NAND теперь не 0 и 1, а 1 и 1 — что дает 0

Шаг 4. На входе верхнего NAND теперь 0 и 0

Триггер при этом фиксируется в новое состояние, которое не меняется.

Рис 3. Вход /S=0; 0,0 на верхнем; 1,1 на нижнем

Что произойдет, если отпустить /S и сделать его 1? Ничего особенного. Просто теперь триггер будет находится в состоянии, как на рис. 1

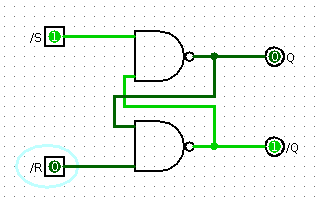

Аналогично работает переброска и в другое состояние:

Рис 4. Вход /R=0; 1,1 на верхнем; 0,0 на нижнем

Работает симметрично переброске /S.

Что по итогу получается. Данный триггер срабатывает при подаче на него 0 либо на /S, и тогда выход Q=1, /Q=0, либо же на /R и в этом случае выход Q=0, /Q=1.

Я рассказал о триггере, основанном на NAND. Если заменить NAND на NOR, то получим ту же схему, только срабатывать такой триггер будет на 1, а не на 0 на входе.

Рис 5. Так выглядит активация /Q=1 при установленном R=1

Таблица истинности NOR:

A B C 0 0 | 1 0 1 | 0 1 0 | 0 1 1 | 0Это как перевернутый в другую сторону AND.

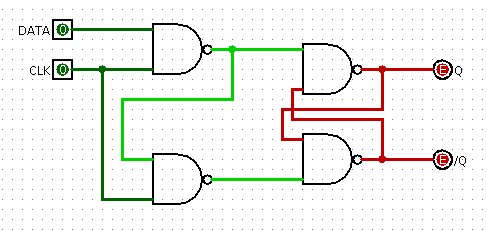

§ Про принцип работы D-триггера

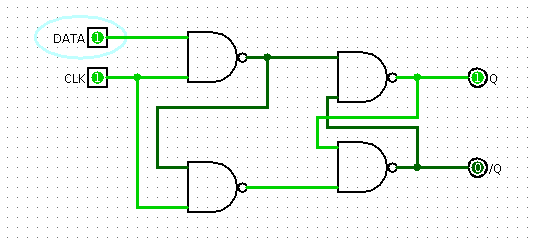

Сразу же приведу его схему с интересными особенностями:

Рис 6. D-триггер на 4-NAND

Поскольку логисим не смог определить состояние выходов NAND у триггера, то он назначил на провода состояние E - ошибочное. Оно поменяется как только появится 0 на одном из входов.

Теперь самый интересный вопрос. Слева и справа реализован демультиплексор, да, именно демультиплексор с инверсной логикой на выходе. Это значит что если CLK=1, то на выходе верхнего левого NAND будет 0 тогда когда D=0, или 0 будет на нижнем при D=1.

Проверим все варианты, при DATA=0, CLK=0 — на рис. 6

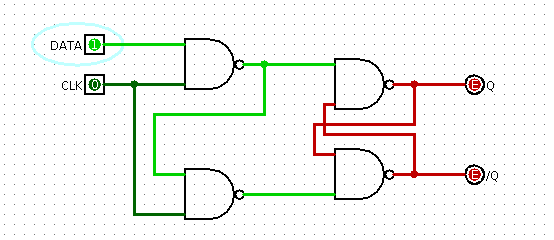

Рис 7. DATA=1, CLK=0, на выходах стабильный 1 и 1

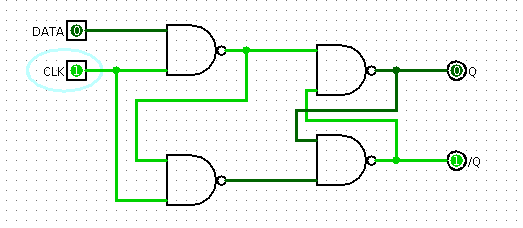

Рис 8. DATA=0, CLK=1, на выходах появляется 1 и 0

Рис 9. DATA=1, CLK=1, на выходах появляется 0 и 1

На этом описание работы D-триггера подходи к логическому концу.

Существует огромное количество разнообразных триггеров разных мастей и вариантов. В данной статье я их описывать не буду, но может быть, оставлю на будущие статьи. Пока что всё.