§ Начало

Итак, пришло время, наконец, создавать процессор, очень похожий на 8088, о создании которого я мечтал годами. У этого процессора будут серьезные отличия от 8088, например, работать он будет на частоте 25 мгц и немного побыстрее по декодированию и исполнению инструкции. До этого материала я уже делал несколько реализации процессора, в том числе делал эмулятор. Сегодня я хочу начать цикл статей по созданию такого процессора снова, с нуля.За основу я выбрал именно 8088, потому что он имеет 8-битную шину данных, ибо, поскольку я не хочу в данный момент погружаться в дебри конвейееров и кешей, то все инструкции будут выполняться просто и последовательно, одна за другой, байт за байтом. Это сэкономит мне время и будет проще воспринять тому, кто все будет читать.

В целом, компьютер будет из себя представлять систему на чипе.

- Сам процессор

- Общая быстрая память - до 300Кб

- Видеопамять - 8Кб

- Контроллер прерываний

- Контроллер PS/2

- Контроллер SPI

- SDRAM

§ Первичный шаблон

Для разработки процессора я традиционно использую отладчик icarus verilog. Начнем, как и обычно, с создания tb.v:`timescale 10ns / 1ns module tb; reg clock; reg clock25; always #0.5 clock = ~clock; always #2.0 clock25 = ~clock25; initial begin clock = 0; clock25 = 0; #2000 $finish; end initial begin $dumpfile("tb.vcd"); $dumpvars(0, tb); end // 1Мб памяти. Простой контроллер памяти // ----------------------------------------- reg [ 7:0] memory[1024*1024]; wire [19:0] address; // Шина адреса reg [ 7:0] i_data; // Входящие данные в процессор wire [ 7:0] o_data; // Исходящие wire we; // Сигнал на запись данных в память always @(posedge clock) begin i_data <= memory[address]; if (we) memory[address] <= o_data; end // ----------------------------------------- endmoduleДобавлен clock25, который генерирует тактовый сигнал в 4 раза медленнее, чем clock. Он и будет использоваться для тактирования процессорного ядра.

В модуле реализовано создание огромного массива памяти

memory размером 1Мб по 8 бит. К проводу address будет подключен процессор, который и будет управлять шиной адреса. Также процессор подключен к i_data — входящими данными в него и o_data — исходящими. Как видно, ввод и вывод данных разделены, а не комбинированы, как это делается в обычных процессорах для экономии пинов. Поскольку это система на чипе (SoC), то здесь так можно сделать.Провод we также контролируется процессором, потому если он =1, то на следующем такте (100 мгц), будет записаны данные o_data по адресу address в память. Здесь память является "плоской", без всяких переименований и перемещений, к тому же, можно записывать в любую ее область, даже в область BIOS. Не знаю, насколько это позволительно так делать, но если что, потом поменяю.

В обработчике always на каждом такте в i_data всякий раз записывается новое значение из памяти по адресу

address.§ Подключение процессорного модуля

Теперь же, чтобы к тестбенчу подключить новый модуль, надо явно указать это в списке подключаемых файлов:iverilog -g2005-sv -DICARUS=1 -o tb.qqq tb.v ps2.v cpu.vМодуль процессора будет находится в cpu.v. Создам новый шаблон для процессора:module cpu ( input clock, // 25 Mhz input reset_n, // =0 Сброс input locked, // =1 Рабочий режим /* verilator lint_off UNDRIVEN */ output [19:0] address, input [ 7:0] i_data, output reg [ 7:0] o_data, output reg we ); initial begin o_data = 8'b0; we = 1'b0; end endmoduleЗдесь сразу скажу, что

verilator lint_off UNDRIVEN нужен для того, чтобы верилятор не ругался на то, что сигнал address ни к чему не подключен. И я могу сказать, что он совершенно справедливо ругается. Потом подключение будет, но пока что так.Помимо уже известных проводов и регистров, на входе есть некоторые пины:

- reset_n - сигнал сброса, когда он равен 0, процессор необходимо сбросить

- locked - стабилизация PLL, если он равен =1, то включить процессор в работу, но помимо этой функции, locked=0 еще при остановке выполнения процессора, когда например, данные все еще не готовы с i_data

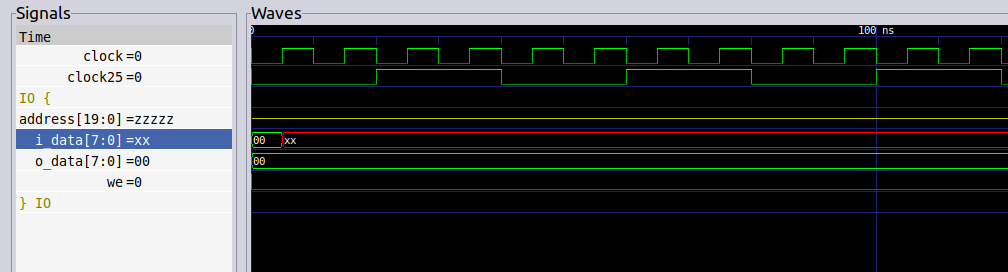

cpu CPU8088 ( .clock (clock25), // 25 Mhz! .reset_n (1'b1), .locked (1'b1), .address (address), .i_data (i_data), .o_data (o_data), .we (we) );Как видно, в тестовых целях, reset_n и locked объявлены в 1, что значит то, что значения были уже проинициализированы правильно. Запустив симуляцию в gtkwave, видим картину маслом:

Тут все красное, ибо address никуда не указывает (он в находится в отключенном состоянии), i_data прочитывает из пустоты, и o_data с we равны 0, потому что они были инициализированы через initial в самом модуле процессора.

§ Связывание с верилятором

Поскольку добавился новый, очень важный модуль, такой как процессор, его надо синтезировать верилятором.Расширяем список синтезируемых верилятором модулей уже до 3-х:

tbc: verilate g++ -o tb -I$(VINC) tb.cc \ $(VINC)/verilated.cpp \ obj_dir/Vvga__ALL.a \ obj_dir/Vps2__ALL.a \ obj_dir/Vcpu__ALL.a -lSDL2 verilate: verilator $(WARN) -cc vga.v verilator $(WARN) -cc ps2.v verilator $(WARN) -cc cpu.v cd obj_dir && make -f Vvga.mk cd obj_dir && make -f Vps2.mk cd obj_dir && make -f Vcpu.mkВстраиваем в tb.cc:

#include "obj_dir/Vcpu.h"И в app.cc добавляется:

protected: ... Vcpu* cpu_mod; ... App() { ... cpu_mod = new Vcpu();То есть, добавляем создание нового класса Vcpu. И в методе tick25():

cpu_mod->clock = 0; cpu_mod->eval(); // В начале ... cpu_mod->clock = 1; cpu_mod->eval(); // В концеВ начале метода добавляется переход clock в 0, а в конце - в clock=1.

Но это еще не все. Процессор, конечно, будет так запущен в работу, но ведь у него нет доступа в память. А это надо организовать.

Вначале я перестрою память и уберу использование vmemory и заменю на memory:

protected: ... unsigned char* memory; ... App() { ... memory = (unsigned char*)malloc(1024*1024); ... void destroy() { ... free(memory);Создается переменная memory, инициализируется, а также не забываем освободить память после завершения программы.

Для видеоадаптера выделяется теперь совершенно другая область памяти, начиная с 0xb8000:

// Загрузить знакогенератор FILE* fp = fopen("font.bin", "rb"); fread(memory + 0xB8000 + 4096, 1, 4096, fp); fclose(fp); // Заполнить чем-нибудь видеобуфер for (int i = 0; i < 4096; i += 2) { memory[0xb8000 + i] = i; // (i>>1) & 255; memory[0xb8000 + i+1] = i+1; //0x17; }Обычно там и находится текстовый видеобуфер. В методе tick25 также не забудем поменять источник данных:

vga_mod->data = memory[ 0xb8000 + vga_mod->address ];Это первый этап. Второй этап это связь процессора с памятью. Для этого потребуется добавить 2 строки:

if (cpu_mod->we) memory[ cpu_mod->address & 0xFFFFF ] = cpu_mod->o_data; cpu_mod->i_data = memory[ cpu_mod->address & 0xFFFFF ];Если есть запись, записать, и потом прочесть новое значение. То есть, если we=1, то после записи из o_data, в i_data появится это значение сразу же.

В данный момент, пока процессор не работает, ничего не будет происходить вообще. Чтобы процессор заработал, предстоит еще очень и очень много чего сделать...

Но на этом пожалуй, я завершу эту статью.

Исходные коды скачать тут.

[Оглавление] [Следующая >>]