§ Создание проекта

Начну я делать проект на Verilog. Для этого я сначала делаю testbench, потом пишу процессор и в конце уже синтезирую на реальной схеме. Писать я буду для микросхему MAX10-02DC, а там памяти только 12кб, но сам код для процессора должен быть универсальным. Я попробую его сделать универсальным и подходящим по таймингам настолько, насколько смогу. Шаблон для testbench я возьму с этой страницы.Итак, создаем папку где-нибудь, складываем файлы из шаблона тестбенча. Делать проект буду на своей любимой частоте 25 МГц и поэтому придется для этого использовать модуль PLL. Но вообще пока что это не требуется, потому что всё будет выполняться в данный момент именно на симуляторе verilog.

§ Модуль процессора

Создам первый шаблонmodule nes6502( input wire clock, output wire [15:0] address, input wire [ 7:0] data, output reg [ 7:0] out, output reg rd, output reg we ); endmodule

- clock будет тактироваться от 25 мгц, но хотя надо 3.5 мгц

- address принимает 64кб, но в реальной схеме у меня только 12кб (или 46кб для ПЛИС Cyclone 3 марсохода)

- data входящие данные из памяти

- out исходящие данные для записи в память

- rd сигнал на чтение данных операнда из памяти, это нужно для PPU для Денди

- we запись в память (write enabled)

// Регистры процессора reg [ 7:0] A; reg [ 7:0] X; reg [ 7:0] Y; reg [ 7:0] P; reg [ 7:0] S; reg [15:0] pc = 16'h0000;Теперь очень важный момент такой, что иногда указатель в память бывает либо с регистра PC, текущего счетчика адреса, либо с некоторого курсора, который извлекает операнд

assign address = bus ? cursor : pc; // Выбор источника памяти reg bus = 0; reg [15:0] cursor;Если bus=0, то указателем в память будет PC, а если bus=1, то регистр cursor.

§ Подключение nes6502 в tb

Теперь надо подключить этот модуль в тестбенч, для этого надо написать следующее объявление в tb.v:wire [15:0] address; reg [ 7:0] data_in; wire [ 7:0] data_out; wire read; wire write; nes6502 NesMeow( .clock (clk25), .address(address), .data (data_in), .out (data_out), .rd (read), .we (write) );А также не забыть указать в makefile новый файл

iverilog -g2005-sv -DICARUS=1 -o tb.qqq tb.v nes6502.v

§ Отладка

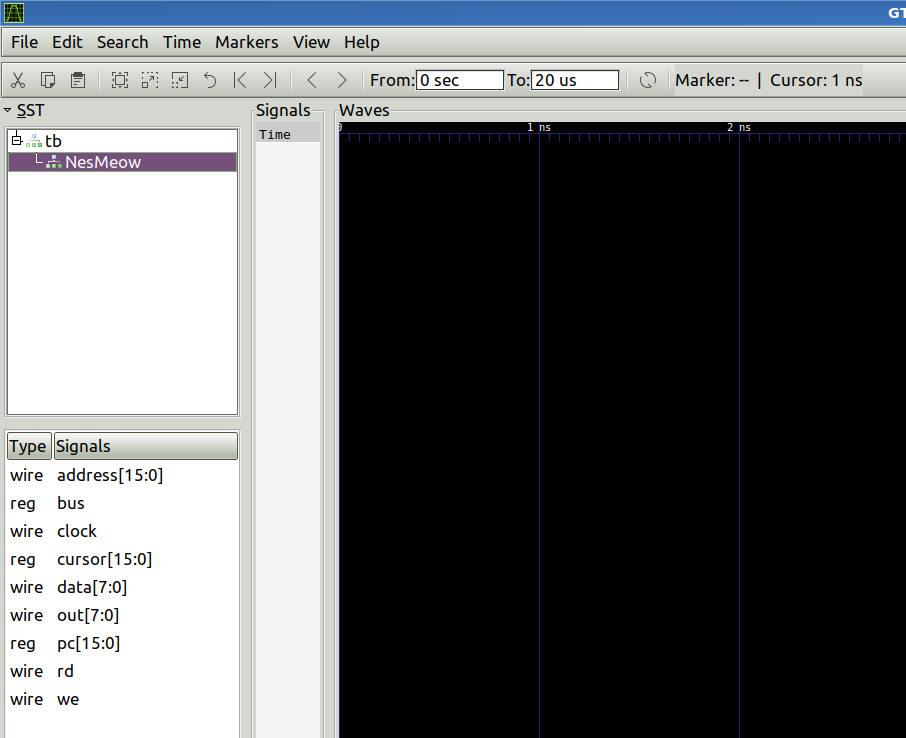

Для отладки надо сначала запустить сгенерированный vcd файл через командуgtkwave tb.vcd и получится окно.

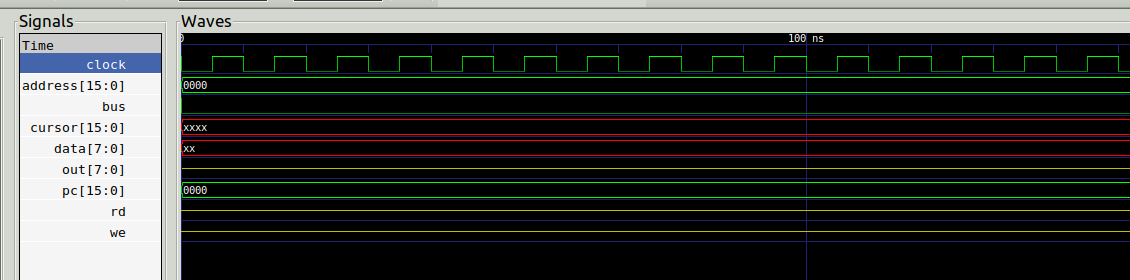

В этом окне я обычно выбираю слева все провода и нажимаю Append, получая систему сигналов

Но тут пока что не на что смотреть, кроме тактовых сигналов.